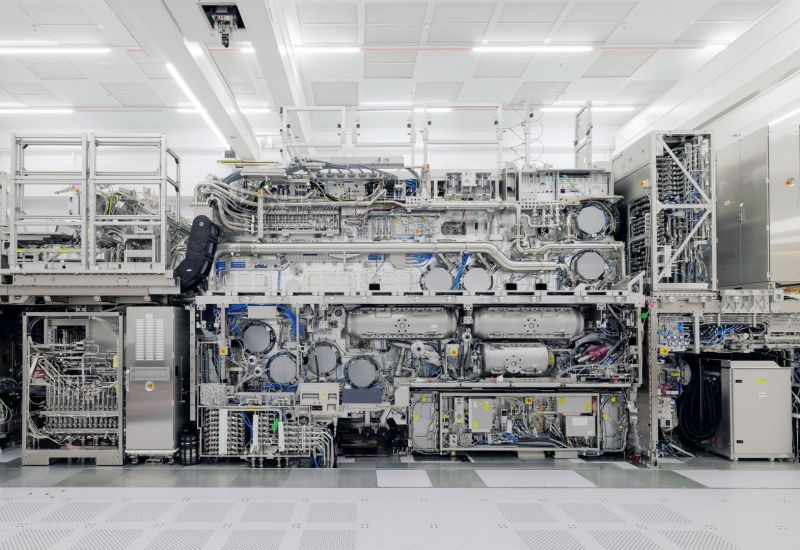

ASMLは、最も薄いチップの大量生産に向けたHigh-NA EUVの最終準備を発表しました

6

software

ASMLは、高数値回折角(High‑NA)技術を持つチップ製造業者の注目を集めている

高数値回折角(High‑NA)スキャナーを使用せずにチップを製造することを計画しているマイクロチップメーカーは、ASMLの新しいリソグラフィシステムに興味を示し始めています。オランダ企業は、テストが装置が量産準備完了であることを示したと確信しています。

技術部門長からの主要データ

ASMLの技術部門長マルコ・ピテルス氏は、Reutersに対し、High‑NA EUVスキャナーのテスト結果が同社にサンノゼで開催される予定のテクノロジーカンファレンスで製品を紹介できることを示したと述べました。最新のスキャナーを用いた試験では、2 nm未満のプロセス技術で約500,000枚のシリコンウェハーを処理することに成功しました。

量産準備状況

これらのスキャナーはそれぞれ約4億ドルと高価ですが、ASMLは「形式的には」量産に適していると主張しています。装置は必要な露光精度を提供し、設定や修理によるダウンタイムが20%未満です。このため、高性能チップのシリーズ生産に適しています。

顧客の適応期間

それでも、顧客はHigh‑NA EUV技術を自社の製造ラインに完全に導入するまでに2〜3年を要します。現在、Intel、TSMC、Samsungといった大手企業がこの装置を検討しています。

今年末までにASMLはダウンタイムを10%に短縮し、スキャナーの効率指標を改善する計画です。同社は顧客に詳細データを共有し、新世代リソグラフィへの移行が合理的であることを納得させる準備ができています。

Asted Cloud

Asted Cloud

コメント (0)

感想を共有してください。礼儀正しく、話題に沿ってお願いします。

コメントするにはログイン