ASMLは、来年から高い数値開口(High‑NA)EUV技術を広範に採用し、トランジスタサイズが1.4 nm以下のチップ製造に取り組む予定です

概要

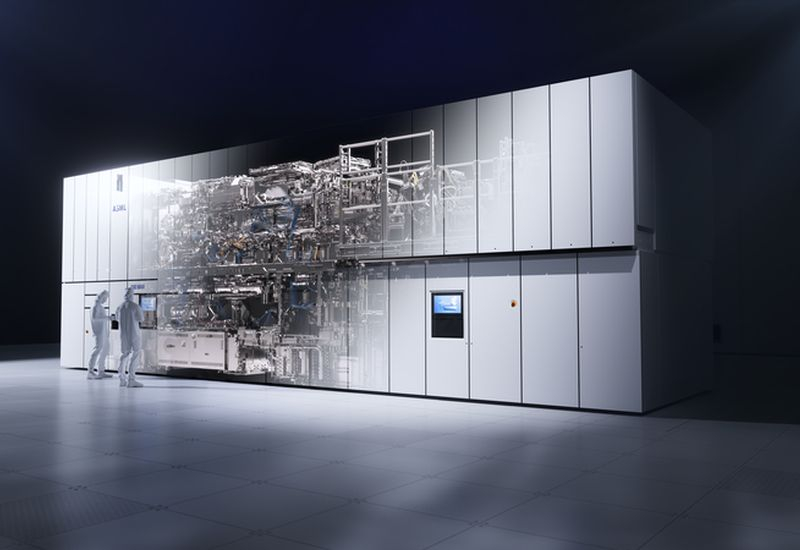

マイクロチップのミニチュア化の新しい段階では、より高度なリソグラフィ手法への移行が必要です。今後2年間で業界はHigh‑NA EUVクラスの装置を使用したチップ製造を開始し、一回通過で最大8 nmまで達成できる技術を導入し、1.4 nm以下および10 nm未満(DRAM)のプロセスへの道を開きます。

1. High‑NA EUVの技術的可能性

パラメータ | 値

数値開口 (NA) | 0.55

一回通過で達成できる最小サイズ | ≤ 8 nm

可能なプロセス | 1.4 nm(集積回路)、< 10 nm(DRAM)

これらの特性により、ASML Twinscan EXE:5200B および同様のソリューションは将来のマイクロエレクトロニクス技術にとって不可欠となります。

2. 主なプレイヤー

企業 | 導入状況 | コメント

ASML | High‑NA EUV 製造業者 | 初期顧客:Intel、Samsung、SK Hynix

TSMC | 大量導入準備中 | 1.4 nmチップの放棄計画あり。2023年12月に Twinscan EXE:5200B を導入し、14A 技術と関連装置のリリースを準備。

Samsung Electronics | 初回スキャナーを2023年12月取得;2番目は今期中に到着予定。Exynos 2600(2 nm)および将来の Tesla プロセッサーで使用計画。

SK Hynix | 2023年9月から High‑NA EUV を習得。DRAM(10 nm)では既に標準EUVリソグラフィを使用し、6世代目には最低5層のEUVを採用予定。

Micron Technology | 導入時期未定。

Rapidus (Japan) | 2 nm 技術を習得中;2029年に1.4 nm を計画。2027年までに北海道で 2 nm チップの大量生産を開始予定。

3. 経済的側面

* 装置コスト – High‑NA EUV システムは約3億8,000万USD。

* より高価な装置への移行は製品単価を上げ、最終的には消費者価格に反映されます。

* そのため、TSMC や Rapidus のような大手メーカーは慎重であり、段階的導入を計画しています。

4. 予想スケジュール

ASML の新しいリソグラフィスキャナーは、2027–2028 年に先進半導体製品の大量生産に積極的に使用され始めます。それ以前に企業は既存プロセスラインを段階的に調整し、High‑NA EUV を統合します。

結論

High‑NA EUV への移行は、1.4 nm およびよりコンパクトな DRAM の実現に向けた重要なステップです。世界最大手の企業はすでに準備を進めていますが、高コストと製造チェーンの適応必要性から、大規模導入には数年を要します。

Asted Cloud

Asted Cloud

コメント (0)

感想を共有してください。礼儀正しく、話題に沿ってお願いします。

コメントするにはログイン