新しいツールはナノメートルトランジスタの欠陥検索を高速化し、プロセスデバッグをより簡単で楽しくします

近代半導体で原子欠陥を観測する新しい方法

コーネル大学の科学者は、ASM社とTSMC社と協力して、高度なチップに隠れた原子レベルの欠陥を可視化できる手法を開発しました。このアプローチは、マイクロチップ製造プロセスのデバッグに特に重要です。欠陥をより正確に評価できれば、不良品が減り、生産成熟までの時間も短縮されます。

研究対象

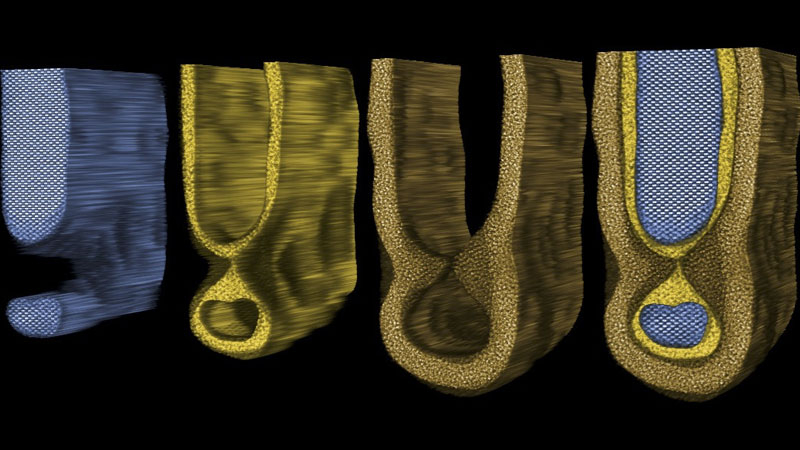

本研究では、ゲート・オール・アラウンド(GAA)トランジスタを備えた処理済みプレートが使用されました。これはチャンネル全体を覆う最新型のゲートです。ベルギーのImecセンターからサンプルが提供されました。各GAAチャネルは、横断面で18個の原子からなる「管状」構造であり、その壁には不均一性や欠け、その他の欠陥が存在し、トランジスタ特性に直接影響します。処理後に構造を変更できないため、研究者は数千ステップにわたる製造段階ごとに品質を追跡し、エラー数を削減することを目指しました。

手法

原子数レベルの欠陥を観測するために、科学者は多平面電子ピチャログラフィ(multislice electron ptychography)を用いました。この方法はサブアングストローム・ナノメートル解像度で材料内部を深さ方向に解析します。電子散乱データを収集し、原子スケールの画像を構築します。

重要なステップは、STEM(走査型透過電子顕微鏡)内のEMPAD検出器を通じて四次元回折データを取得することです。その後、位相再構成と多くの「スライス」にわたる電子伝搬シミュレーションが行われます。従来の投影法とは異なり、ピチャログラフィは一組の測定から完全な体積構造を復元し、個々の原子位置、格子局所変形、およびフェーズ境界パラメータを正確に特定できます。

メリット

- 欠陥スペクトルの質的・量的評価が可能になり、従来は間接手法しか利用できませんでした。

- 開発初期段階で技術的問題を迅速に検出し解決できるようになります。

- TSMCなど大手企業の関心が確認されており、現代チップ製造のデバッグに実用価値があります。

この新しい方法は、高度な半導体製造における品質管理をより信頼性と効率的にする道を開きます。

Asted Cloud

Asted Cloud

コメント (0)

感想を共有してください。礼儀正しく、話題に沿ってお願いします。

コメントするにはログイン